Page 47 - 컴퓨터구조(프로그래밍 관점에서 바라보는)도서 미리보기

P. 47

CHAPTER 6? 컴퓨터 하드웨어 195

LSB(가장 오른쪽 비트)부터 들어오며, 연속되는 클럭을 통해서 4개의 플립

플랍으로 각 비트들이 옮겨가게 된다(shift). 그렇지만 출력은 현재의 값이

모두 동시에 병렬적으로 출력된다.

Q0 Q1 Q2 Q3

DATA D Q DQ DQ DQ

CK CK CK CK

CK

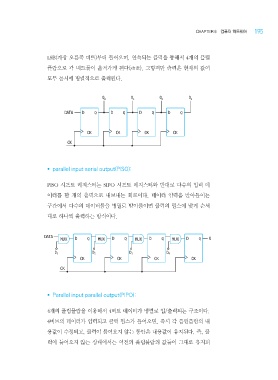

?? parallel input serial output(PISO):

PISO 시프트 레지스터는 SIPO 시프트 레지스터와 반대로 다수의 입력 데

이터를 한 개의 출력으로 내보내는 회로이다. 데이터 입력을 받아들이는

구간에서 다수의 데이터들을 병렬로 받아들이면 클럭의 펄스에 맞게 순서

대로 하나씩 출력하는 방식이다.

DATA MUX D Q MUX D Q MUX D Q MUX D QQ

D3 D2 D1 D0 CK

CK CK CK CK

?? Parallel input parallel output(PIPO):

4개의 플립플랍을 이용해서 4비트 데이터가 병렬로 입/출력되는 구조이다.

4비트의 데이터가 입력되고 클럭 펄스가 들어오면, 즉시 각 플립플랍의 내

용값이 수정되고, 클럭이 들어오지 않는 동안은 내용값이 유지된다. 즉, 클

럭이 들어오지 않는 상태에서는 이전의 플립플랍의 값들이 그대로 유지되